Digital Combination Lock

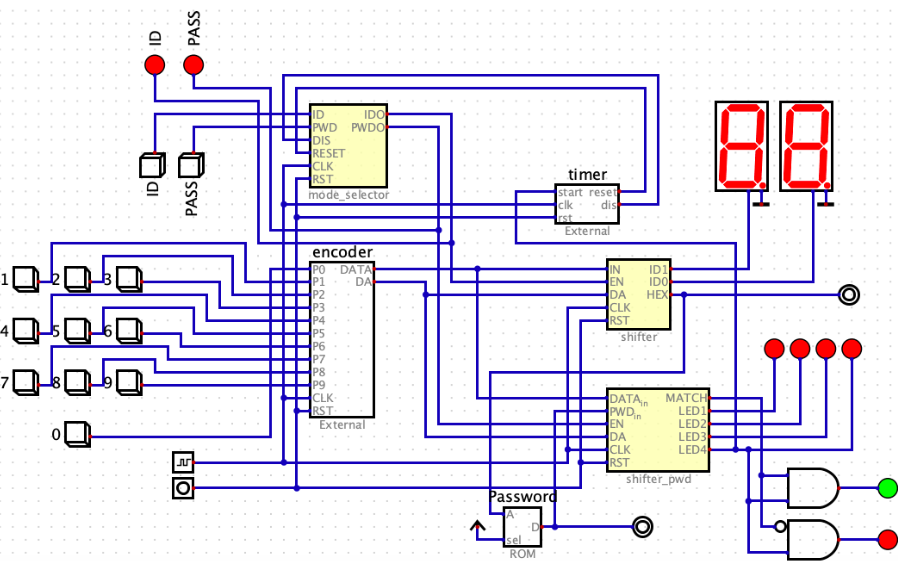

A hardware-level digital combination lock designed using Algorithmic State Machine (ASM) methodology and implemented in Verilog. The project involves designing the controller FSM, mapping out the circuitry pathway, and simulating the lock behavior, demonstrating expertise in digital logic design and hardware description languages.

Tech Stack

The Problem

Designing secure digital lock systems at the hardware level requires precise state machine design and thorough verification to ensure the lock cannot be bypassed or stuck in invalid states.

Approach

Used ASM methodology to design the finite state machine controller. Implemented the design in Verilog with a modular architecture separating the datapath and control unit. Verified correctness through simulation and formal verification using Prolog for logic validation.

Key Challenges

- Ensuring all edge cases are handled in the FSM to prevent lock bypass

- Timing verification for reliable sequential input detection

- Mapping the ASM chart to synthesizable Verilog code

Results

Delivered a fully functional digital combination lock with verified FSM behavior, demonstrating mastery of hardware design principles and HDL programming.